过去半年以来,以DeepSeek等大语言模型在各行各业的应用与普及为例,AI大模型发展浪潮席卷全世界,并在图像识别、内容生成、创意设计、辅助开发、对话等领域展现出无尽可能。

经历了卷积神经网络模型(CNN)、自注意力模型(Transformer)等阶段,目前AI大模型正在不断升级学习能力,往多模态、扩展上下文等方向进一步发展,这对模型运算量与训练数据集都提出了更高要求。而对整个AI算力硬件生态而言,除最核心的算力芯片外,存储、通信(传输)技术同样成为支撑AI大模型进化与应用的基石。

那么我们今天就着眼于存储领域,一起了解哪些关键、新锐的存储技术,能够服务于行业级的AI大模型发展与综合应用。

NVIDIACEO在过去数年经常提到“摩尔定律已死”,当时多数人理解其意指半导体的制程工艺逼近极限,且普遍带来成本失控,此类因素成为传统计算性能发展的瓶颈。而在AI大模型的时代重新审视这一观点,我们看到的则是大模型的训练需求,与单位成本算力增长的不匹配等现象。

面对现实的压力,AI行业从多种路径展开探索,避免让摩尔定律成为“逐渐收紧的枷锁”,由此诞生了模型量化训练、稀疏化、新模型架构等突破算力束缚的创新,我们熟悉的DeepSeek也是其中闪耀的成果之一。

存储领域也面临相似的压力,而传统的SRAM、DRAM存储在容量、带宽上的性能迭代不仅落后于AI对算力的需求,甚至也没能赶上相邻两代芯片间算力的迭代。很多时候AI训练的瓶颈往往不在芯片本身的运算能力,而在于数据从存储子系统传输至运算单元的过程。

因此,行业将目光放在2013年就已亮相的HBM技术上。

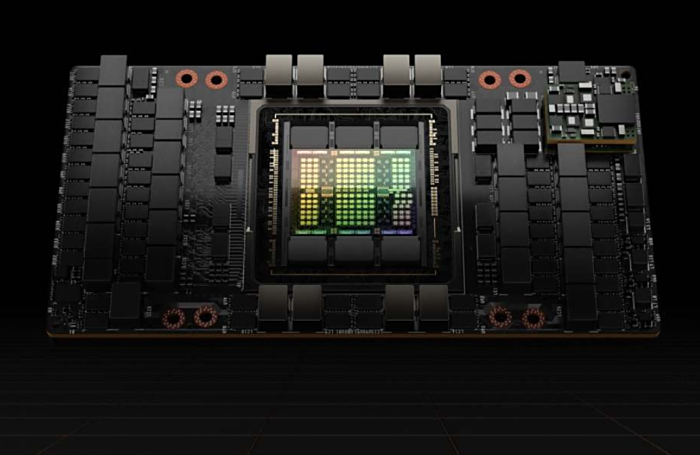

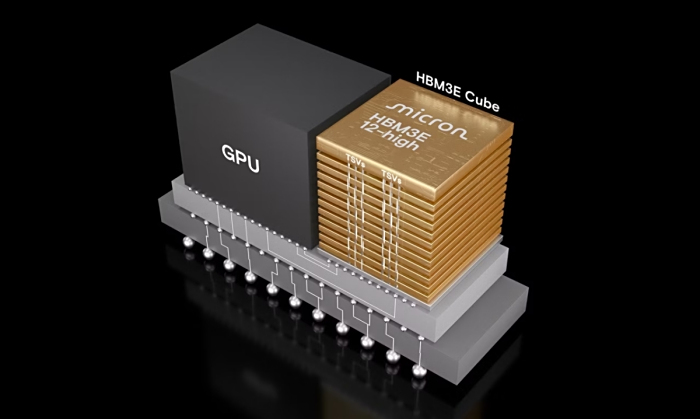

诞生于十多年前的HBM可以说长期处于不温不火的状态,这可能是因为它在当时有点超前了:相比常规的DRAM内存,HBM采用垂直堆叠排列的多片DRAM芯片,并使用硅通孔(TSV)技术连接,相当于使3D堆叠规模突破了单颗flash的物理尺寸限制,进一步提升容量、带宽。

同时HBM也使用不同于传统DRAM的PCB走线、插槽连接等方式,而是以类似SRAM的方式借助硅中介层直接与计算芯片进行通信,在同一基板上的信号传输路径缩短为毫米级,进一步降低延迟、功耗,并提升信号完整性。

由此,相比常规的DRAM类型,例如DDR5内存、GDDR6/GDDR7显存等,HBM实现了更大的容量、总线位宽与实际带宽。我们可以从一些存储企业网站上得知,目前应用于前沿算力芯片的HBM3E能够达到单颗24GB容量、1.2TB/s带宽与2.5倍于常规DRAM的单位能效。

达到如此优越的性能自然也有其代价,首先是硅通孔TSV与硅中介层的制造与封装技术带来相比传统DRAM成倍增长的极高成本;其次,多层堆叠也为HBM制造带来不少良率上的问题;最后是多层堆叠的立方体形态,使其应用面限于AI计算、数据中心等行业级领域的计算硬件,无法像传统DRAM一样扩展至消费级的设备与市场,以规模效应降低生产成本。

值得一提的是,中国企业目前仍处于HBM的堆叠、封装、材料、通信、制造设备等关键技术研发攻关阶段,尚未实现HBM的量产,同时在国际上也面临国外存储企业的专利壁垒,面临多重挑战。但行业乐观估计,中国企业在多项关键材料与技术上已形成积累,随着专项政策资金的持续投入,产业链协同攻关,有望在5年内实现HBM领域从“跟跑”到“并跑”的突破。

全闪存阵列:低延迟、高并发、高吞吐需求带来的必然趋势

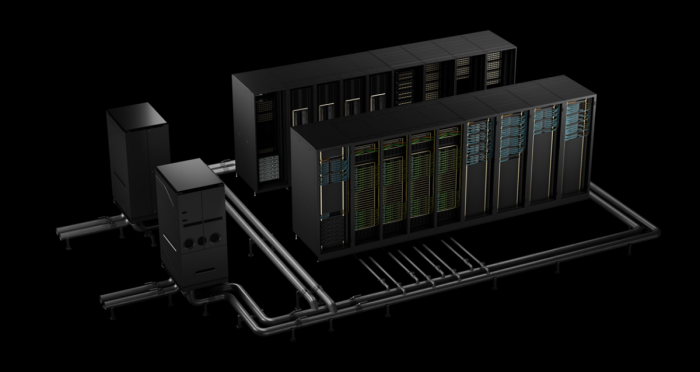

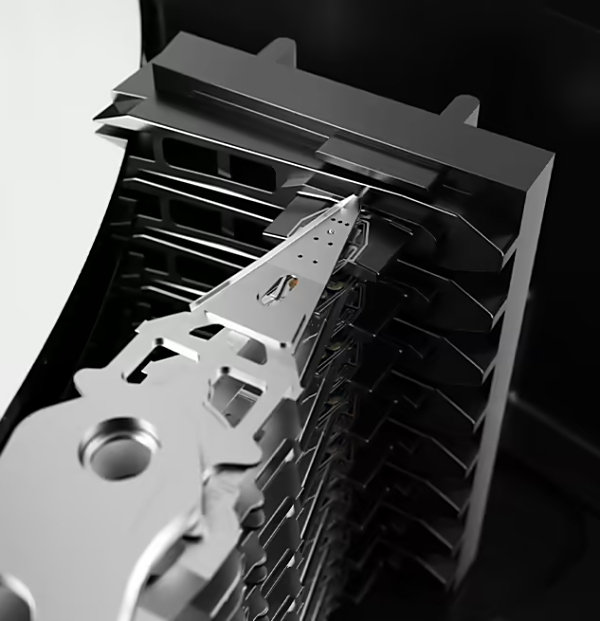

HBM为高性能AI计算解决了DRAM(动态随机存储器)性能方面的问题,自然也需要一种方案解决NVM(非易失性存储器)的性能问题,通俗类比我们的PC来说,内存性能到顶了,硬盘总不能用个普普通通的吧?拥有突出性能优势的全闪存阵列技术,因此成为高性能数据中心的必然趋势。

基于NVMe协议的全闪存阵列,相对于传统的串行连接SCSI接口(SAS)协议拥有多种优势,首先是存储介质从机械硬盘(HDD)全面转向固态硬盘(SSD),这一点针对系统整体的轻量化、低功耗、高能效等趋势,影响不言而喻。主机借助NVMeoverFabrics技术,还能通过网络实现高性能的远程存储访问。

全闪存阵列应用了更快的总线接口、更大的队列深度,简化了传统SAS中的多次协议交互,缩短服务器与存储阵列数据传输的路径,能够满足AI计算对低时延、高并发、高吞吐的严苛需求。更多新技术也正解决固态硬盘在行业级应用中的固有问题,例如均衡磨损算法,通过ZNS技术抑制写入放大等。

不过近期还有一则耐人寻味的新闻。国际机械硬盘巨头希捷公布2025财年第四财季与完整财年业绩,其中第四财季收入同步增长29.52%,财年营收同比增长38.86%。希捷在第四财季的出货容量达162EB,环比增长13%,平均单盘容量达13TB。

机械硬盘巨头创纪录的盈利增长,似乎反映出行业对大容量机械硬盘的需求依然强劲。不过我们也可以猜测,也许未来AI等高性能计算场景与云端及边缘计算场景等在存储市场上的分野会更加显著。

固态硬盘的通道规格似乎再一次领先了平台性能,从通道速率再次翻倍带来的优势方面,PCIeGen6的64GT/s速率能够为数据中心、AI、智能网联汽车等多种前沿领域所需的高性能计算集群提供更高吞吐量,进一步带来参数同步效率与大模型训练效率的提升。

另一方面,PCIeGen6同样能够为CXL3.0协议提供高性能基础,支持计算芯片以更高速率直接访问分布式内存池,突破硬件自身的内存瓶颈。PCIeGen6还带来新的动态电源管理等节能特性,支持L0p、L1.2低功耗状态,可根据负载进行动态的链路宽度调整。

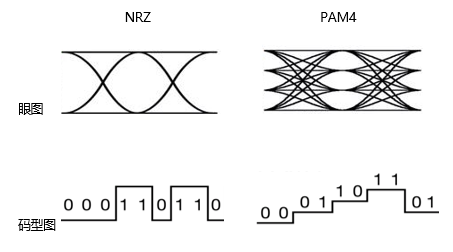

不过PCIeGen6的新特性也带来更多挑战,它首次采用PAM4多电平信号调制,单位时间信号传输的密度翻倍,同时对信噪比的要求更高,因此集成了可动态启用的前向纠错(FEC)功能。